Behavioral Systemverilog Module For 4-to-1 Decoder

- Verilog Code For 8 To 1 Multiplexer Using Dataflow Modelling

- Behavioral Systemverilog Module For 4-to-1 Decoder 2

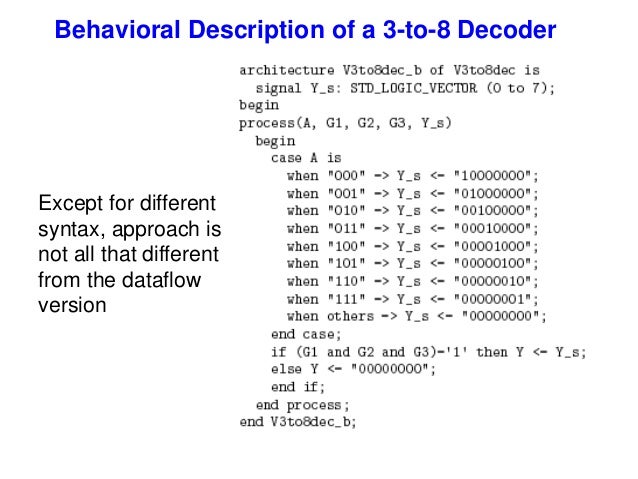

Verilog HDL Abstraction Levels. Behavioral Models: Higher level of modeling where behavior of logic is modeled.

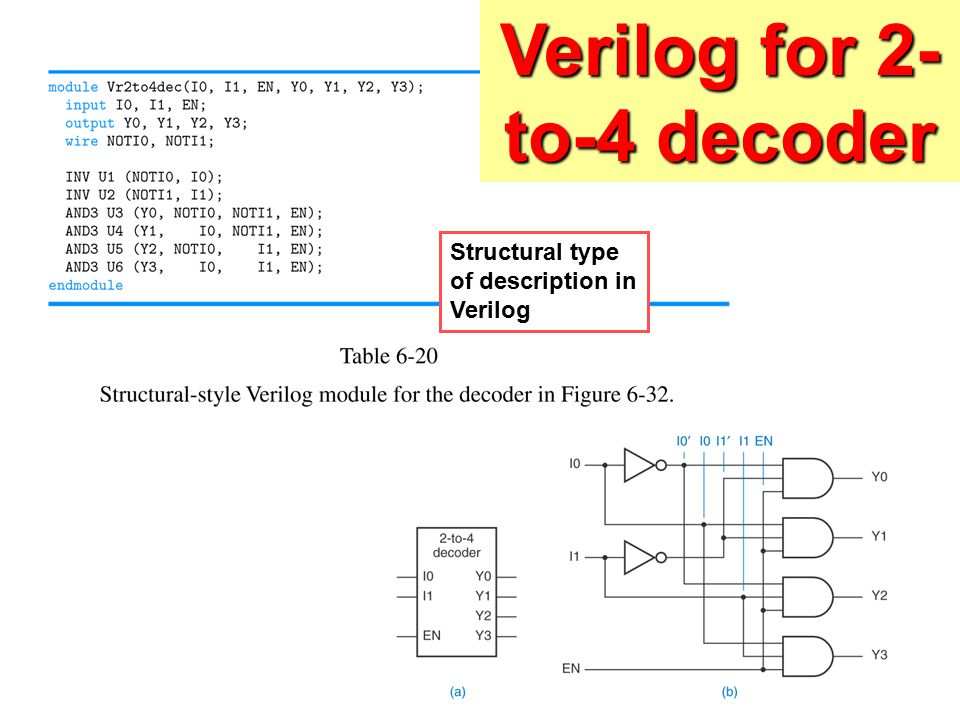

Jul 15, 2013 2: 4 Decoder using Logical Gates (Verilog CODE). Half Subtractor Design using Logical Expression (V. 1: 4 Demultiplexer Design using Gates (Verilog CO. 4 to 1 Multiplexer Design using Logical Expression. Full Subtractor Design using Logical Gates (Verilo. Full Adder Design using Logical Expression (Verilo.

Verilog Code For 8 To 1 Multiplexer Using Dataflow Modelling

RTL Models: Logic is modeled at register level. Structural Models: Logic is modeled at both register level and gate level.Procedural BlocksVerilog behavioral code is inside procedure blocks, but there is an exception: some behavioral code also exist outside procedure blocks.

Behavioral Systemverilog Module For 4-to-1 Decoder 2

We can see this in detail as we make progress.There are two types of procedural blocks in Verilog:. initial: initial blocks execute only once at time zero (start execution at time zero). The sims 4 pc gameplay. always: always blocks loop to execute over and over again; in other words, as the name suggests, it executes always.Example - initial1 module initialexample;2 reg clk,reset,enable,data;3 4 initial begin 5 clk = 0;6 reset = 0;7 enable = 0;8 data = 0;9 end 10 11 endmodule You could download file initialexample.vIn the above example, the initial block execution and always block execution starts at time 0. Always block waits for the event, here positive edge of clock, whereas initial block just executed all the statements within begin and end statement, without waiting.Example - always1 module alwaysexample;2 reg clk,reset,enable,qin,data;3 4 always @ ( posedge clk)5 if (reset) begin 6 data.